Xilinx FPGA Slave-SelectMAP 配置说明及硬件 & 驱动补全

-待更新-

前言

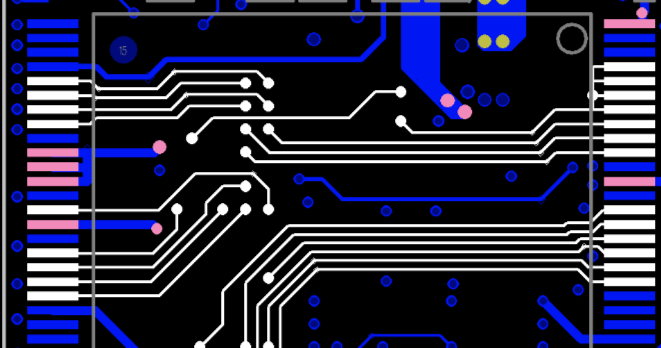

为补全原理图所作工作,NI 家只开源了部分原理图。Xilinx 系列的配置方式较多,这里只进行主控 K7 的配置模式 Slave-SelectMAP 的完善。

Slave-SelectMAP 配置连接方式

如下图所示,上电后 Microprocessor/CPLD 从 Memory Source 中读取程序并通过一定的方式将其下载到 7 系列 FPGA 中。

其中 Memory Source 一般采用 NOR Flash,中间的 Microprocessor/CPLD 一般来说不限,只要能满足时序要求即可,考虑到 CPLD 引脚没那么多,笔者选择 另一块 FPGA 来连接,此时 NOR FLash 充当的角色为该 FGPA 外设。

在这种配置方式下,引脚 M[2: 0] = 110,上下拉电阻参考手册,值得注意的是 JTAG 模式在任意条件下都可。

| Configuration Mode | M[2:0] | Bus Width | CCLK Direction |

|---|---|---|---|

| Master Serial | 000 | x1 | Output |

| Master SPI | 001 | x1, x2, x4 | Output |

| Master BPI | 010 | x8, x16 | Output |

| Master SelectMAP | 100 | x8, x16 | Output |

| JTAG | 101 | x1 | Not Applicable |

| Slave SelectMAP | 110 | x8, x16, x32(1) | Input |

| Slave Serial(2) | 111 | x1 | Input |

时序配置见参考。此外需注意高低电平要求。

NOR Flash 和 Microprocessor/CPLD 连接方式

连接方式参考手册,满足读写要求即可,需注意高低电平要求。

NOR Flash 更新方式

使用 JTAG Flash Programmer 利用JTAG接口和现有的各种仿真器来控制芯片,通过改变一组I/O状态,模拟总线时序来烧写。

支持 USB to JTAG interfaces based on FTDI FT2232 chip。

- 暂未验证是否支持 Gowin

参考

7 系列 FPGA 配置手册

- 中文:https://gitcode.com/Open-source-documentation-tutorial/3399e/blob/main/UG470中文.pdf

- 英文:https://fpga.eetrend.com/files-eetrend-xilinx/download/201408/7594-13761-ug4707seriesconfig.pdf

NOR Flash 参考手册

- IS29GL256 :https://item.szlcsc.com/datasheet/IS29GL256-70FLET/1327426.html?spm=sc.it.xds.a___sc.gb.xh1.zy.n&lcsc_vid=TgNcVlZWFgJYUVECTlIMBlZURAIKV1cAQllZBFcDRFIxVlNSR1ZaUVRRQVBaXzsOAxUeFF5JWAgaAglIBBsCBBcFWQIBCks%3D

- S29GL256P:https://item.szlcsc.com/datasheet/S29GL256P10TFI010/472067.html?spm=sc.it.xds.a___sc.gb.xh2.zy.n&lcsc_vid=TgNcVlZWFgJYUVECTlIMBlZURAIKV1cAQllZBFcDRFIxVlNSR1ZaUVRRQVBaXzsOAxUeFF5JWAgaAglIBBsCBBcFWQIBCks%3D

- PCB布局指南:https://www.infineon.com/dgdl/Infineon-AN216200_Infineon_Non-Burst-Mode_Parallel_NOR_Flash_Memory_Layout_Guide_for_PCBs-ApplicationNotes-v02_00-CN.pdf?fileId=8ac78c8c7cdc391c017d0d2cace86437

其他相关

- 时序配置参考 1:https://opencores.org/websvn/filedetails?repname=phr&path=%2Fphr%2Ftrunk%2Fdoc%2Freferences%2Fxilinx%2Fapplication_notes%2Fxapp502.pdf&rev=90

- 时序配置参考 2:https://blog.csdn.net/qq_40863150/article/details/132191283

- BPI Flash 说明:https://blog.csdn.net/weixin_62432906/article/details/130348110

- 使用 JTAG Flash Programmer 烧写 Flash:https://blog.csdn.net/a1232345/article/details/41891669

- TopJTAG Flash Programmer 官网:http://www.topjtag.com/flash-programmer/

- Device/Package xc7k410tffg900:https://china.xilinx.com/content/dam/xilinx/support/packagefiles/k7packages/xc7k410tffg900pkg.txt

This piece of writing is an original article, utilizing theCC BY-NC-SA 4.0Agreement. For complete reproduction, please acknowledge the source as Courtesy ofSoCoco's Blog

Comment